Home

Decodificador para Display de 7 Segmentos em VHDL

- Detalhes

- Categoria: Exemplos com CPLD

- Publicado em Quarta, 09 Maio 2012 11:04

- Escrito por João Marcos de Aguiar

- Acessos: 7892

Decodificador para Display de 7 Segmentos em VHDL

Este artigo apresentará o desenvolvimento de um decodificador binario para display de 7 segmentos implementado em VHDL, que apresentará o valor hexadecimal no display. O projeto foi testado no ModelSim-Altera, através de um testbench.

Figura 1: Bloco decodificador de 7 segmentos

Componentes utilizados:

- 1x Kit CPLD;

- 1x Placa display de 7 segmentos, anodo comum;

- 1x Placa de chaves.

Descrição do Funcionamento

O decodificador receberá um dado binário de quatro bits e apresentará na saída os sinais necessários para a visualização do algarismo hexadecimal correspondente ao dado de entrada no display de 7 segmentos. A tabela abaixo mostra os algarismos e os sinais necessários para que o display mostre o algarismo. Vale lembrar que se o display fosse do tipo catodo comum, as saídas presisariam receber o valor inverso.

Tabela 1: Tabela da verdade para o decodificador (valida para anodo comum).

Diferentemente do projeto em modo esquemático, no modelamento em VHDL comportamental não é necessário a elaboração do circuito lógico correspondente, basta descrever o seu funcionamento. Isso é muito útil quando se trata de projetos com mais complexos, nos quais é muito difícil elaborar o circuito. No VHDL, apresenta-se a descrição do circuito via programação e o compilador elabora o circuito correspondente.

Descrição em VHDL

Inicialmente, é necessário declarar as bibliotecas que serão utilizadas durante o código VHDL. As bibliotecas STD e work são declaradas implicitamente e não precisam ser declaradas novamente no VHDL. As demais bibliotecas precisam ser declaradas. A biblioteca ieee merece destaque por ser amplamente usada.

Além de declarar as bibliotecas, ainda é necessário declarar quais os pacotes da biblioteca serão utilizados. Na biblioteca ieee vale destacar os pacotes std_logic_1164, std_logic_unsigned, o numeric_std e o std_logic_arith. O primeiro define o tipo std_logic, normalmente utilizado para declarar os sinais do projeto.

Abaixo segue a declaração das bibliotecas e pacotes para este projeto:

Em seguida é necessário declarar a entidade do projeto. A entidade apresenta as entradas e saídas do projeto, sendo praticamente modelando um bloco. Além das entradas e saídas, podem ser feitas declarações genéricas, onde são declaradas constantes que podem ser referenciadas durante o código e podem ser alteradas facilmes muandando os seus valores na declaração de entidade. Neste projeto não será utilizado essa declaração. A entrada do circuito será um dado de 4 bits, declarado como um veto de std_logic numerados de 3 a 0.A saída será os 7 sinais para o display de 7 segmentos.

Depois da declaração da entidade, será declarado a arquitetura. A arquitetura descreverá o funcionamento do projeto. Dentro dela podem ocorrer intruções concorrente ou sequencialmentes. As intruções sequenciais ocorrem em dentro da estrutura "process". Neste programa apenas utilizaremos intruções concorrentes.

Dentro da arquitetura são declarados sinais, que funcionam como ligações internas do projeto. Os sinais precisam ser declarados depois da declaração da arquitetura e antes do inicio da descrição do comportamento, como mostrado abaixo.

Será utilizado como sinal um vetor com 7 std_logic, os quais serão utilizados na decodificação e passaram o valor correspondennte para a saída.

Em seguida será feita as intruções do decodificador. Utilizaremos a estrutura with-select para fazer a decodificação. Essa estrutura analisa o valor de uma expressão ou dado e, dependendo desse valor, atribui um valor para a saída. Neste projeto, o dado a ser analisado é a entrada DADO, e a saída será o sinal declarado na arquitetura.

Por ultimo, faz-se a atribuição dos valores do sinal para as saídas:

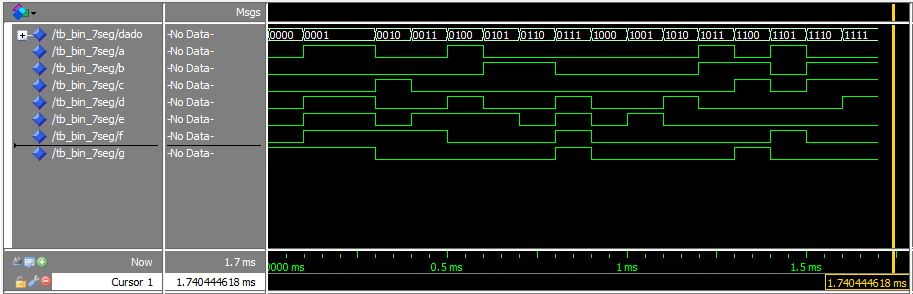

Simulação

A simulação pode ser feita de através do modo interativo ou via testebench. Para este projeto utilizaremos um testbench. O inicio do testbench é similar ao VHDL do projeto. Primeiro declara-se as bibliotecas que serão utilizadas (normalmente as mesmas do projeto) e depois a entidade do testbench, que não possui entradas nem saídas.

Em seguida faz-se a declaração da arquitetura e a declaração dos sinais. Os sinais foram nomeados igualmente ao aos nomes utilizados no projeto, porém isso não é necessários.

Depois de declarar os sinais, faz-se a instanciação da UUT (unity under test - Unidade sob teste, tradução livre). Nesse ponto, é necessário que os sinais sejam declarados na ordem em que são declarados na UUT, independente de nomes, porém é necessário que sejam do mesmo tipo.

Com a UUT instanciada, pode-se dar as instruções de teste. Utilizaremos um processo, estrutura onde os comando são executados sequencialmente, para fazer a simulação. No testbench foram colocadas todas os possiveis valores de DADO (de 0 a F). Abaixo segue algumas atribuições:

No final do processo e da simulação é necessário, respectivamente, de um "end process;" e "end architecture;". Após completar o testbench, execute uma analise e síntese. Agora é preciso configurar o projeto para compilar o testbench quando a ferramenta de simulação for chamada. Siga o tutorial a seguir feito no wink:

COLOCAR TUTO WINK

Figura 2: Simulação do Projeto

Estrutura Física

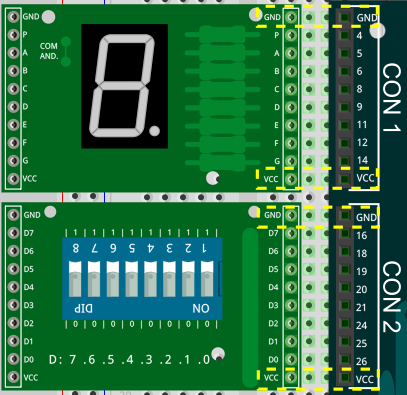

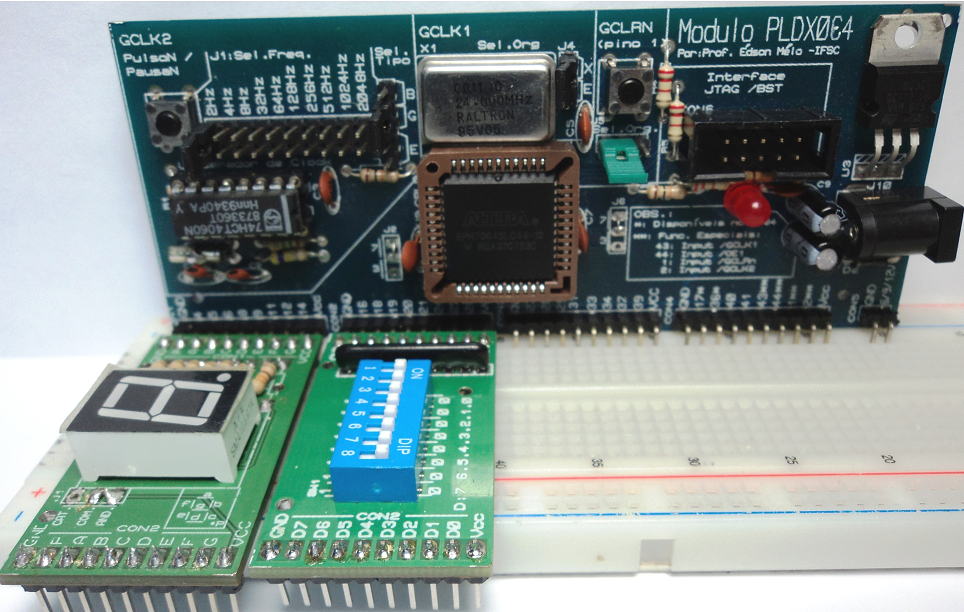

O projeto é composto pelo módulo de CPLD, uma placa de display de sete segmentos de anodo comum e outra de chaves, conectados respectivamente no CON1 e no CON2 do CPLD, como mostra a Figura 10. Lembre-se de que o CPLD usado é o EPM7064, da família MAX7000S.

No projeto, as entradas são implementadas pela placa de chaves, as saídas pela placa de display e as funções lógicas pelo kit de CPLD.

Figura 10: Estrutura Física do Projeto

Montagem e Roteamento

Fique atento para que o Vcc e o GND dos periféricos fiquem alinhados com o do CPLD. Veja em detalhe a ilustração da montagem do projeto, feita no Fritzing, na Figura 11.

Figura 11: Ligação na Matriz de Contatos

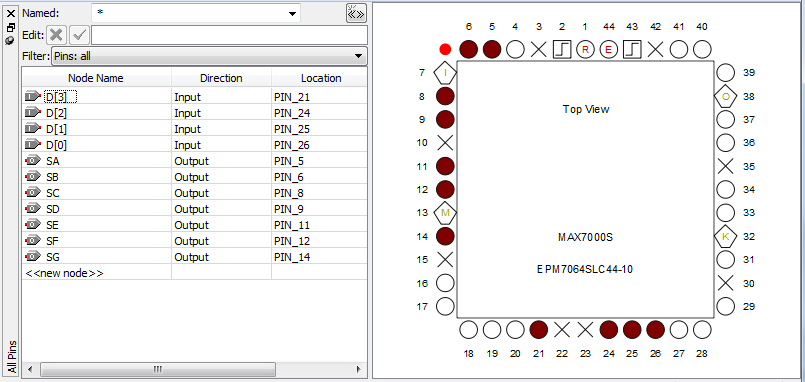

A Figura 12 mostra a pinagem atribuida no Pin Planner, no Quartus II, de acordo com a ligação na matriz de contatos.

Figura 12: Atribuição de Pinos no Pin Planner

Gravação e Teste

Depois de implementar e atribuir os pinos do projeto, faça uma "Compilação Completa" para gerar o arquivo de gravação do projeto, além do programa procurar algum erro ou aviso no mesmo.

Para gravar o projeto siga o Tutorial de Criação de Projeto em Modo Esquemático na etapa de "Gravação do CPLD" clicando aqui. Lembre-se sempre de gravar o módulo de CPLD sem os periféricos, evitando problemas na pinagem atribuída em projetos anteriores. Também não esqueça de configurar as saídas não utilizadas como entradas tri-state.

Para testar o funcionamento desse projeto, monta-se a periferia como relatada na "Estrutura Física" e atribuem-se níveis lógicos na placa de chaves, analisando a combinação posta com a decodificação no display de sete segmentos. O vídeo na introdução desse exemplo apresenta o teste realizado.