Decodificador para Display de Sete Segmentos

- Detalhes

- Categoria: Exemplos com CPLD

- Publicado em Quinta, 02 Fevereiro 2012 14:27

- Escrito por Marcos Vinícius Leal da Silva

- Acessos: 6633

Decodificador para Display de Sete Segmentos

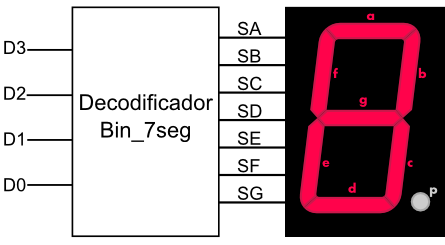

O objetivo do projeto a seguir é, a partir de um código binário de 4 bits, exibir o algarismo correspondente em hexadecimal em um display de sete segmentos de anodo comum. A Figura 1 mostra o bloco representativo deste projeto. Sua aplicação é basicamente quando precisamos mostrar algum algarismo, sendo muito utilizado em nossos projetos.

Figura 1: Bloco Decodificador Bin_7seg

Este artigo será um exemplo em modo esquemático de um circuito combinacional no software Quartus® II, utilizando apenas componentes primitivos do mesmo. A simulação será feita pelo modo interativo no ModelSim®-Altera.

Neste projeto será utilizado:

- 1x Módulo CPLD_7064;

- 1x Placa de Chaves;

- 1x Placa de Display de Sete Segmentos de anodo comum.

Lógica de Funcionamento

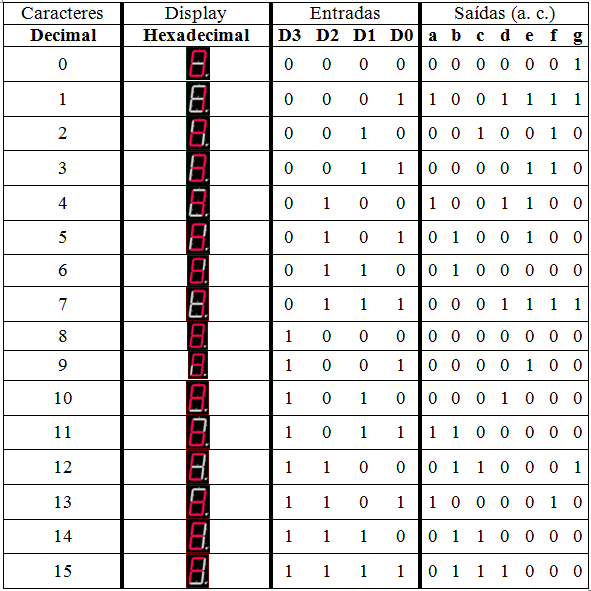

Este circuito possui quatro entradas (D3, D2, D1 e D0), formando um código binário de 4 bits, e sete saídas, para os segmentos do display (a, b, c, d, e, f, g). A partir do código fornecido pela entrada, o decodificador interpreta-o e seleciona quais saidas atribuir nível lógico alto, ou seja, quais segmentos serão "apagados" (devido ao display ser de anodo comum), de acordo com a Tabela da Verdade do projeto.

Tabela 1: Tabela da Verdade do Decodificador Bin_7seg

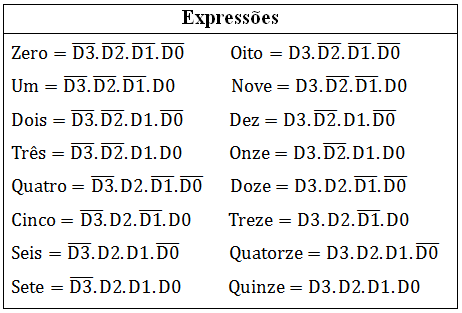

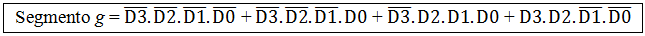

As expressões lógicas abaixo são obtidas a partir das entradas da Tabela da Verdade.

Tabela 2: Expressões Lógicas

Analisando a Tabela 1 constatamos, por exemplo, que o segmento "a" não acende (e portanto, a saída "a" deve ser nivel lógico alto) nos caracteres 1, 4, 11 e 13. Assim:

- Segmento a = Um + Quatro + Onze + Treze

Seguindo esse mesmo raciocínio para os outros segmentos, podemos formular as seguintes expressões lógicas:

- Segmento b = Cinco + Seis + Onze + Doze + Quatorze + Quinze

- Segmento c = Dois + Doze + Quatorze + Quinze

- Segmento d = Um + Quatro + Sete + Dez + Quinze

- Segmento e = Um + Três + Quatro + Cinco + Sete + Nove

- Segmento f = Um + Dois + Três + Sete + Treze

- Segmento g = Zero + Um + Sete + Doze

Substituindo os termos das expressões lógicas acima com as expressões da Tabela 2, como demonstrado na Figura 2, obtemos as combinações de níveis lógicos desejados em cada segmento para cada caractere.

Figura 2: Substituição dos termos pelas expressões

Entrada do Projeto em Modo Esquemático

Neste exemplo, abordaremos a implementação do diagrama de blocos de forma sucinta. Para sanar possíveis dúvidas e aprender sobre esse tipo de implementação, acesse a Parte II do "Tutorial de Criação de Projeto em Modo Esquemático".

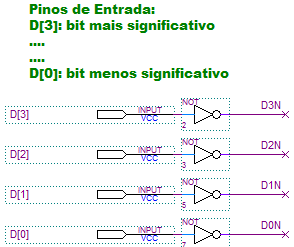

No Quartus® II, comece estruturando o projeto atribuindo as entradas (input) e suas as portas lógicas inversoras (not), ligando e nomeando seus terminais de acordo com a figura abaixo.

Figura 3: Entradas do Projeto

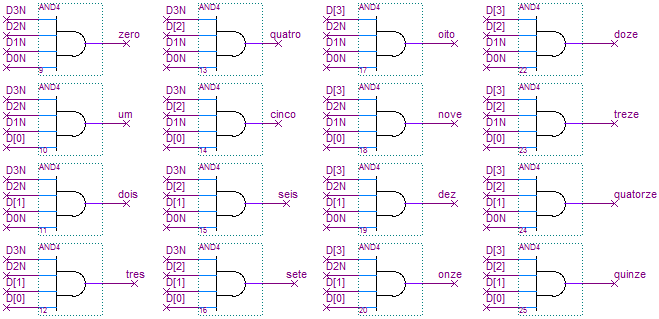

Feito isso, posicione dezesseis portas lógicas "E" de quatro entradas (and4), para todas combinações indicadas na Tabela 2, e nomeie seus terminais como ilustrado na Figura 4.

Figura 4: Portas Lógicas "E"

Finalmente posicione sete portas "OU", para cada segmento, sendo quatro portas lógicas de seis entradas (or6) e outras três portas lógicas de quatro entradas (or4). Adicione também as saídas (output) do projeto, nomeando seus terminais, juntamente com o das portas lógicas, como ilustrado na Figura 5.

Note que os segmentos " d " e " f " possuem cinco variáveis, porém não há porta lógica "OU" com cinco entradas nos componentes primitivos do Quartus® II. Por isso, na implementação lógica desses segmentos, usamos portas lógicas "OU" com seis entradas e "aterramos" uma delas (Figura 5), ou seja, atribuímos nível lógico baixo em uma das entradas.

Figura 5: Portas Lógicas "OU" e Saídas do Projeto

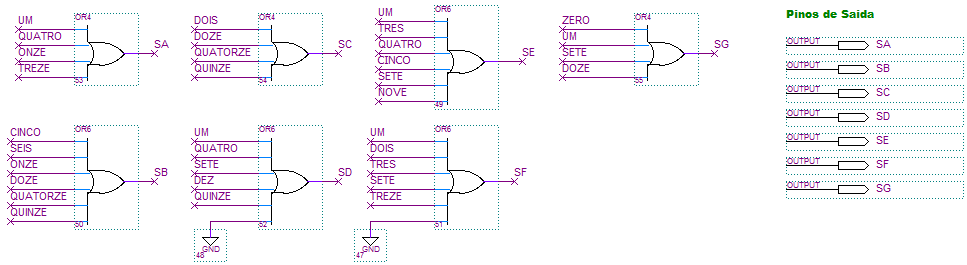

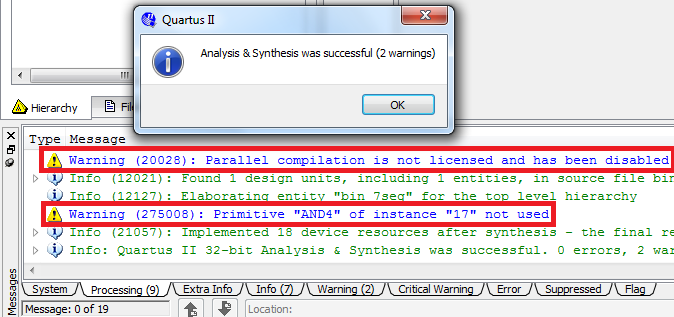

Depois de estruturar todo projeto, faça uma Análise e Síntese do mesmo para poder simulá-lo, além do programa procurar algum erro ou aviso no esquemático. Se não ocorreu nenhum equívoco na implementação do projeto, apenas dois avisos (warnings) serão encontrados: compilação paralela e da porta lógica "E" respectiva à combinação "oito" não usada. Os mesmos podem ser vistos na Figura 6.

Figura 6: Avisos da Análise e Síntese

Não se preocupe com o primeiro aviso, pois essa ferramenta de compilação paralela é acessível somente no software pago. Já o último aviso é válido, pois repare que no algarismo oito nenhum segmento do display precisa ser "apagado", então não usamos aquela porta lógica posteriormente. Porém vamos deixá-lo por comodidade, já que não atrapalhará o funcionamento.

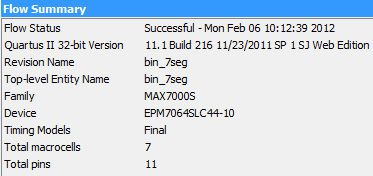

Um resumo da Análise e Síntese está logo abaixo.

Figura 7: Resumo da Análise e Síntese

Simulação

Como esse projeto foi feito em diagrama de blocos, precisamos converte-lo em um código VHDL para simulá-lo no software ModelSim®-Altera. A simulação foi realizada em modo interativo. Aprenda a converter o diagrama de blocos em VHDL e simular pelo modo interativo no tutorial do artigo sobre Simulação Interativa com o ModelSim-Altera.

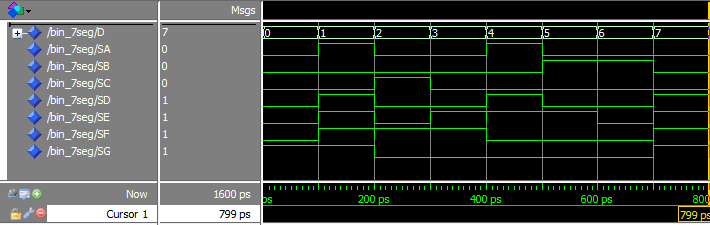

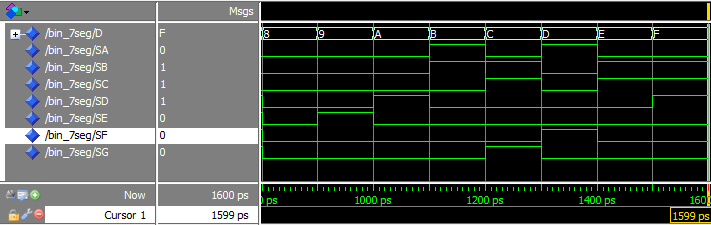

Na simulação, atribuímos níveis lógicos nas entradas e verificamos se os níveis lógicos das saídas, ou seja, de cada segmento, estão de acordo com a lógica do projeto. Por exemplo, quando atribuímos "0011", sendo o algarismo 3, apenas os segmentos "e" e " f " estarão em nível lógico alto (apagados), enquanto todos os outros ficam em nível lógico baixo (acesos). As Figuras 8 e 9 mostram o resultado das simulação. Examine que no algarismo 8, todos os segmentos estão em nível lógico baixo (acesos), confirmando o que foi relatado a pouco.

Figura 8: Resultado da Simulação no ModelSim®-Altera

Figura 9: Resultado da Simulação no ModelSim®-Altera

Estrutura Física

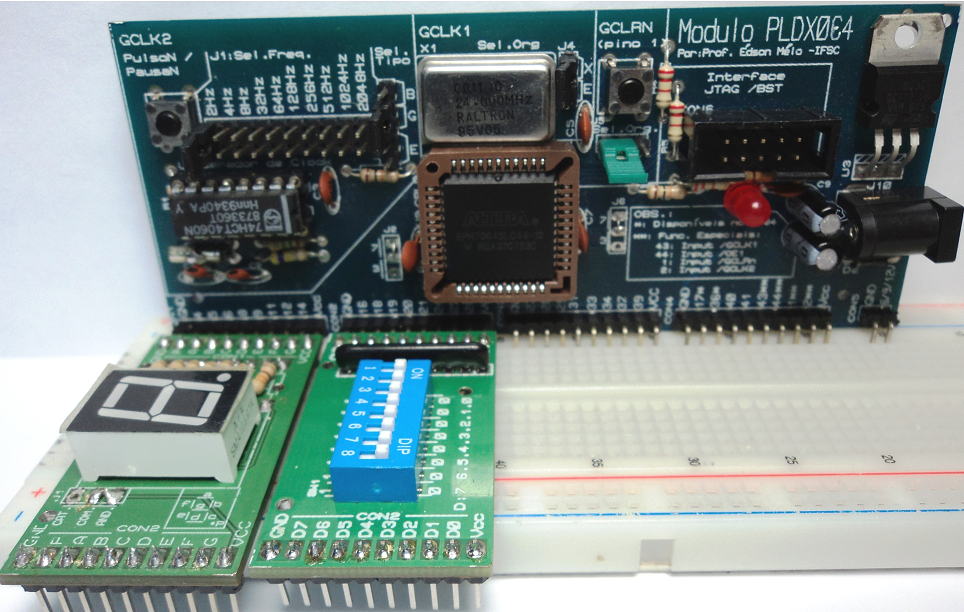

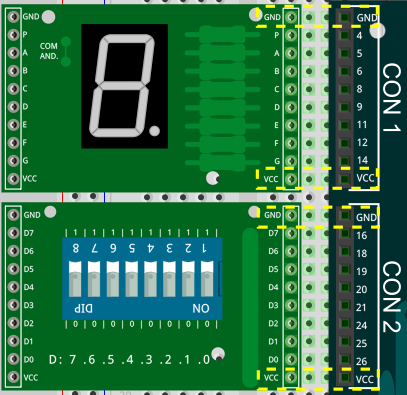

O projeto é composto pelo módulo de CPLD, uma placa de display de sete segmentos de anodo comum e outra de chaves, conectados respectivamente no CON1 e no CON2 do CPLD, como mostra a Figura 10. Lembre-se de que o CPLD usado é o EPM7064, da família MAX7000S.

No projeto, as entradas são implementadas pela placa de chaves, as saídas pela placa de display e as funções lógicas pelo kit de CPLD.

Figura 10: Estrutura Física do Projeto

Montagem e Roteamento

Fique atento para que o Vcc e o GND dos periféricos fiquem alinhados com o do CPLD. Veja em detalhe a ilustração da montagem do projeto, feita no Fritzing, na Figura 11.

Figura 11: Ligação na Matriz de Contatos

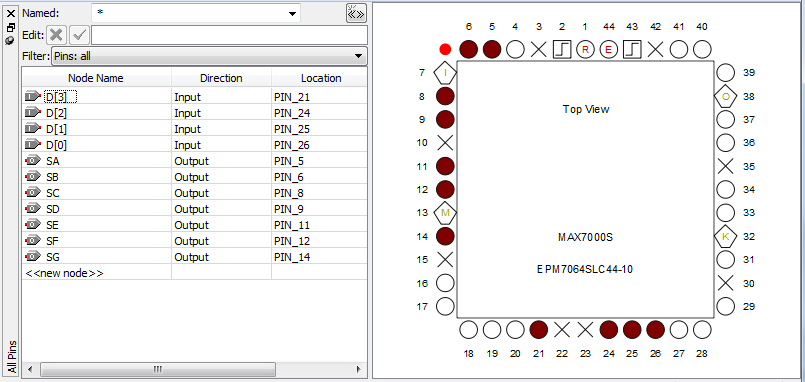

A Figura 12 mostra a pinagem atribuida no Pin Planner, no Quartus II, de acordo com a ligação na matriz de contatos.

Figura 12: Atribuição de Pinos no Pin Planner

Gravação e Teste

Depois de implementar e atribuir os pinos do projeto, faça uma "Compilação Completa" para gerar o arquivo de gravação do projeto, além do programa procurar algum erro ou aviso no mesmo.

Para gravar o projeto siga o Tutorial de Criação de Projeto em Modo Esquemático na etapa de "Gravação do CPLD" clicando aqui. Lembre-se sempre de gravar o módulo de CPLD sem os periféricos, evitando problemas na pinagem atribuída em projetos anteriores. Também não esqueça de configurar as saídas não utilizadas como entradas tri-state.

Para testar o funcionamento desse projeto, monta-se a periferia como relatada na "Estrutura Física" e atribuem-se níveis lógicos na placa de chaves, analisando a combinação posta com a decodificação no display de sete segmentos. O vídeo na introdução desse exemplo apresenta o teste realizado.

Arquivos do Projeto

Para o download do projeto completo, clique aqui.

O arquivo está no formato ".zip", e inclui os arquivos de projeto do Quartus (".qpf"), de modo esquemático (".bdf"), de modo VHDL para simulação (".vhd"), de gravação do CPLD (".pof"), de símbolo para usar em projetos mais avançados (".bsf"), entre outros.

Referências