- Detalhes

-

Categoria: Exemplos com CPLD

-

Publicado em Quinta, 16 Fevereiro 2012 17:25

-

Escrito por Andre Vinicius Rocha Silva

-

Acessos: 2724

Animação VGA

No modo VGA a tela é dividida em pontos (pixels) que são separados por linhas e colunas. Geralmente a imagem possui 480 linhas e 600 colunas e somente um pixel é aceso de cada vez. Para formarmos uma tela, utilizamos o efeito da persistência da visão utilizado também no projeto Multiplexação de display de 6 algarismos.É extremamente recomendável que leia-se a página do Padrão de Cores VGA pois este projeto está intimamente ligado a ele.

O projeto descrito a seguir é um exemplo de circuito lógico sequencial, descrito em VHDL e simulado software ModelSim®-Altera, utilizando um testbench.

Os equipamentos necessários para a implementação do projeto são:

- 1x Kit CPLD 7064;

- 1x Monitor com porta VGA;

- 1x Placa de interface VGA;

- 1x Adaptador para matriz de contatos

Lógica de Funcionamento

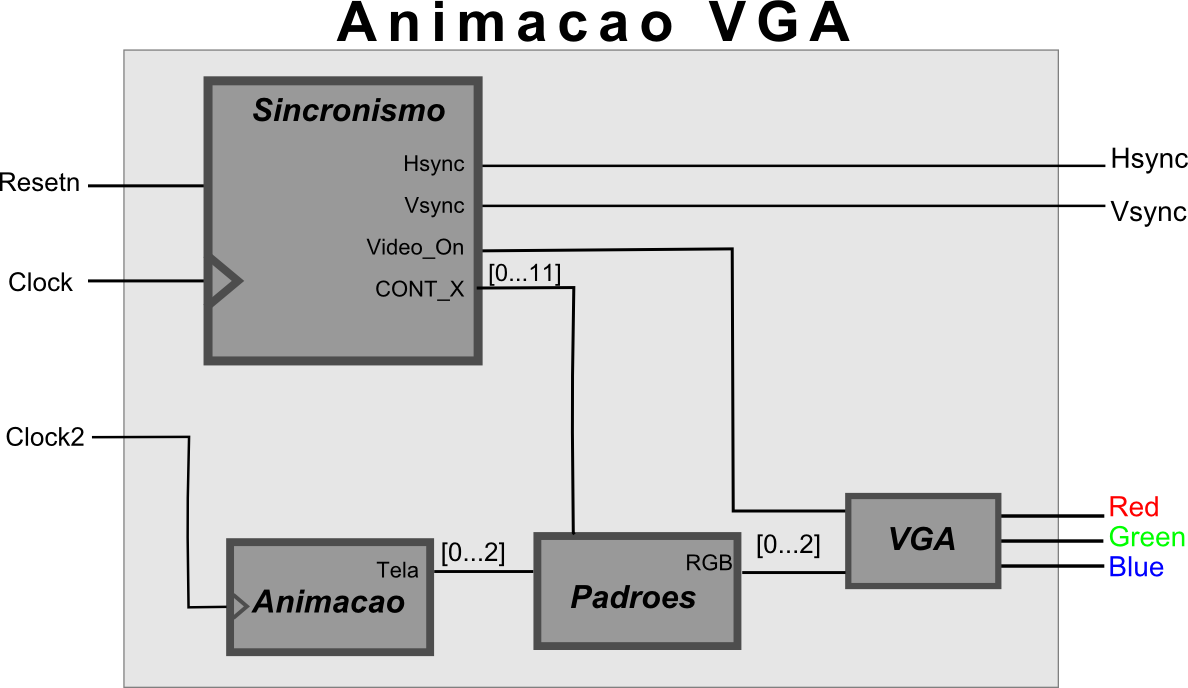

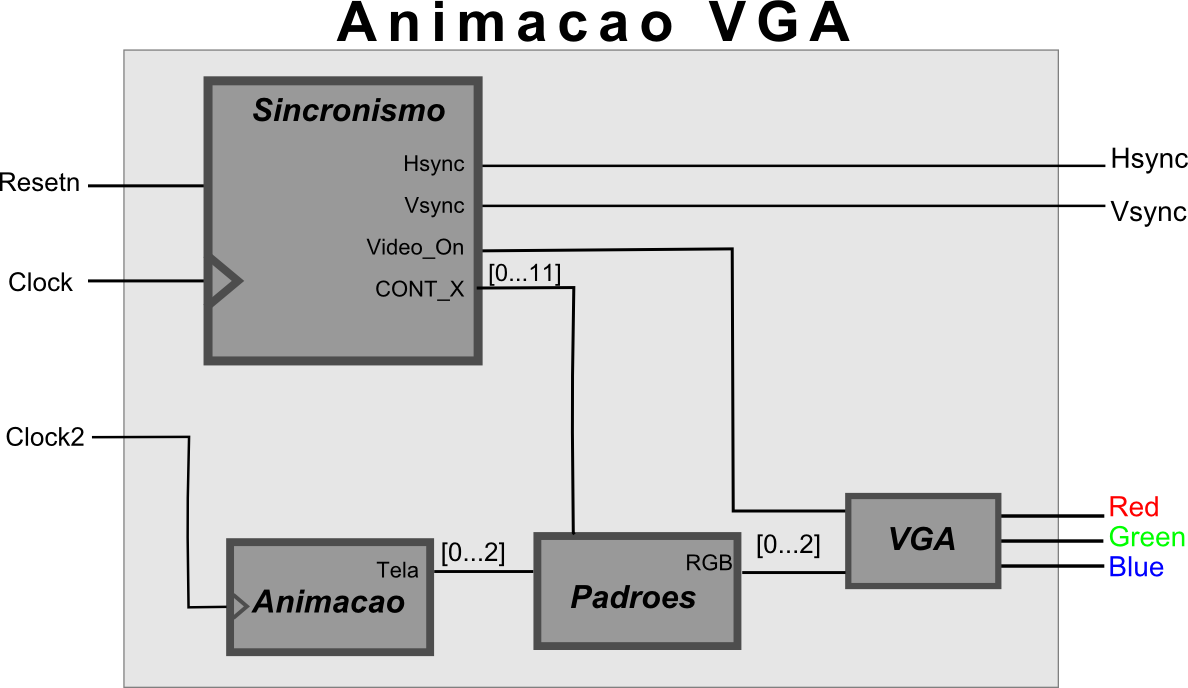

Este projeto difere do Padrão de Cores em apenas dois aspectos. Possui um contador de baixa frequência e um mutiplexador que avalia o estado da contagem.

Figura 1 - Diagrama de blocos

Animação

Um bloco conta os pulsos do clock de baixa frequência (Clock2). O valor do contador é transmitido pelo sinal Tela, que varia de 0 a 5 e é lido pelo bloco Padrões.

ANIMACAO: process(CLOCK2)

begin

if (CLOCK2'event) and (CLOCK2='1') then

if RESET = '1' then

TELA <= "000";

else

if TELA = "101" then

TELA <= "000";

else

TELA <= TELA + "001";

end if;

end if;

end if;

end process ANIMACAO;

Padrões

Um mutiplexador seleciona o tipo de padrão a ser mostrado no monitor a partir do valor (Tela) apresentado pelo contador.

PADROES: process(CLOCK2,CONT_X)

begin

case TELA is

when "000" =>

if CONT_X <100 then

RGB <= "001";

end if;

if (CONT_X>=100 and CONT_X<200) then

RGB <= "010";

end if;

if (CONT_X>=200 and CONT_X<300) then

RGB <= "011";

end if;

if (CONT_X>=300 and CONT_X<400) then

RGB <= "100";

end if;

if (CONT_X>=400 and CONT_X<500) then

RGB <= "101";

end if;

if (CONT_X>=500) then

RGB <= "110";

end if;

when "001" =>

if CONT_X <100 then

RGB <= "010";

end if;

if (CONT_X>=100 and CONT_X<200) then

RGB <= "011";

end if;

if (CONT_X>=200 and CONT_X<300) then

RGB <= "100";

end if;

if (CONT_X>=300 and CONT_X<400) then

RGB <= "101";

end if;

if (CONT_X>=400 and CONT_X<500) then

RGB <= "110";

end if;

if (CONT_X>=500) then

RGB <= "001";

end if;

when "010" =>

if CONT_X <100 then

RGB <= "011";

end if;

if (CONT_X>=100 and CONT_X<200) then

RGB <= "100";

end if;

if (CONT_X>=200 and CONT_X<300) then

RGB <= "101";

end if;

if (CONT_X>=300 and CONT_X<400) then

RGB <= "110";

end if;

if (CONT_X>=400 and CONT_X<500) then

RGB <= "001";

end if;

if (CONT_X>=500) then

RGB <= "010";

end if;

when "011" =>

if CONT_X <100 then

RGB <= "100";

end if;

if (CONT_X>=100 and CONT_X<200) then

RGB <= "101";

end if;

if (CONT_X>=200 and CONT_X<300) then

RGB <= "110";

end if;

if (CONT_X>=300 and CONT_X<400) then

RGB <= "001";

end if;

if (CONT_X>=400 and CONT_X<500) then

RGB <= "010";

end if;

if (CONT_X>=500) then

RGB <= "011";

end if;

when "100" =>

if CONT_X <100 then

RGB <= "101";

end if;

if (CONT_X>=100 and CONT_X<200) then

RGB <= "110";

end if;

if (CONT_X>=200 and CONT_X<300) then

RGB <= "001";

end if;

if (CONT_X>=300 and CONT_X<400) then

RGB <= "010";

end if;

if (CONT_X>=400 and CONT_X<500) then

RGB <= "011";

end if;

if (CONT_X>=500) then

RGB <= "100";

end if;

when others =>

if CONT_X <100 then

RGB <= "110";

end if;

if (CONT_X>=100 and CONT_X<200) then

RGB <= "001";

end if;

if (CONT_X>=200 and CONT_X<300) then

RGB <= "010";

end if;

if (CONT_X>=300 and CONT_X<400) then

RGB <= "011";

end if;

if (CONT_X>=400 and CONT_X<500) then

RGB <= "100";

end if;

if (CONT_X>=500) then

RGB <= "101";

end if;

end case;

end process PADROES;

Outros blocos

Outros blocos, simulação e montagem do projeto são iguais ao projeto Padrão VGA.

Arquivos de Projeto

Para o download do projeto completo, clique aqui.

O arquivo está no formato "zip", e inclui, entre outros:

- O arquivo de projeto do Quartus , no formato ".qpf"

- A descrição no formato VHDL , no formato".vhd"

- O arquivo para gravação do CPLD, no formato ".pof".

- O test bench utilizado na simulação , no formato ".vhd"