Leitura Assíncrona de Teclado

- Detalhes

- Categoria: Exemplos com CPLD

- Publicado em Sexta, 16 Setembro 2011 19:27

- Escrito por João Marcos de Aguiar

- Acessos: 4317

Leitura Assíncrona de Teclado

{youtube}z-c2xbODBlU|480|320|1{/youtube}

O projeto a seguir pretende fazer a leitura de um teclado matricial sem a utilização de clock. Basicamente, quando uma tecla é pressionada o circuito identifica qual a linha e coluna correspondente e decodifica a tecla.

O presente artigo apresenta um exemplo de projeto feito em VHDL de um circuito sequencial, o qual foi simulado no Modelsim-Altera®, utilizando como entrada de dados da simulação um testbench.

Animação 1: Ilustração do projeto apresentado

Nesse projeto será utilizado:

- 1x Módulo CPLD_7064;

- 1x Módulo de teclado matricial;

- 1x Placa de LEDs, para vizualizar o valor da tecla pressionada.

Descrição do Funcionamento

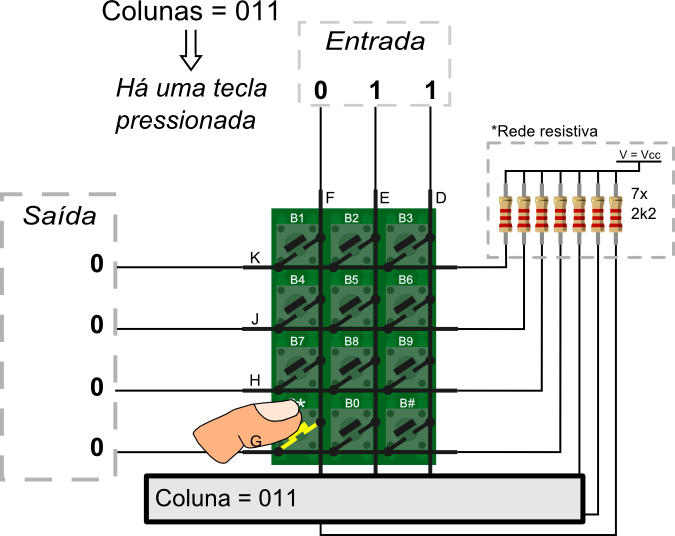

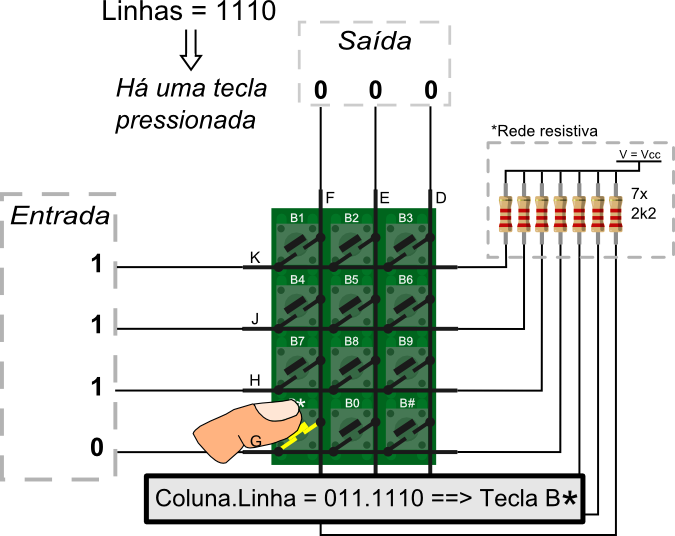

O objetivo do projeto, como foi apresentado acima, é fazer a leitura de um teclado matricial de forma assíncrona. Para isso definem-se as linhas como saídas, em nível lógico baixo, e as colunas como entradas, que devido ao pull-up estarão nível lógico alto fraco (em VHDL,"H").

Quando uma tecla é pressionada estabelece uma conexão entre uma linha e coluna (cada botão está associado a uma diferente combinação de linha e coluna). Então, o estado lógico '0' da linha é transmitido para a coluna. Esta condição deve ser detectada para registrar o estado das colunas (e portanto em que coluna se encontra o botão pressionado).

Descrição em VHDL

No projeto serão utilizados as linhas e colunas como sinais bidirecionais (inout) e um sinal de saída chamado TECLA:

Dentro da architecture se usará um sinal para armazenar os valores das linhas e uma maquina de estados:

O projeto pode ser dividido em três partes: atuação, máquina de estados e decodificação.

O projeto deve atuar quando houver variação no teclado, ou seja, quando houver mudanças em alguma das linhas ou colunas. Dessa forma o processo só precisa ser sensível a variações deles:

Dentro do processo, a atuação dependerá do estado da máquina de estado, nesse caso chamada de teclado. Caso teclado esteja no estado ATIVA_COLUNA, registra-se o valor das colunas e muda o estado para ATIVA_LINHA. Caso esteja em ATIVA_LINHA, verifica se a tecla foi solta, se sim troca o estado para ATIVA_COLUNA, se não continua em ATIVA_LINHA.

A máquina de estado definirá, dependendo do estado, se as colunas/linhas serão entradas ou saídas e precisa ser sensível a mudança no valor de teclado:

Por último, o decodificador analisa os valores obtidos e atribui a TECLA o valor correspondente. Note que não é necessário um sinal para registrar o valor das linhas, pois basta tomar diretamente os valores de entrada.

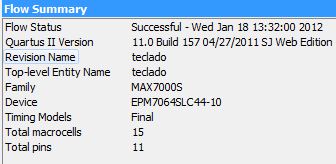

Figura 3: Resultado da analise e sintese.

Simulação

Para verificar o funcionamento do projeto, basta simular o pressionamento de alguns botões e averiguar se a saída é a equivalente ao botão apertado. Para isso, pode-se elaborar um testbench (caso você não saiba fazer um testbench clique aqui) e utilizar o simulador Modelsim-Altera. Abaixo será descrito o código utilizado.

Neste testbench serão simulados as teclas '5', '9', '*'. Note que inicialmente se atribui a todas as linhas e colunas nível lógico alto fraco, para simular o pull-up e para simular o botão solto, após ser pressionado, se atribui novamente 'H' nas coordenadas correspondentes:

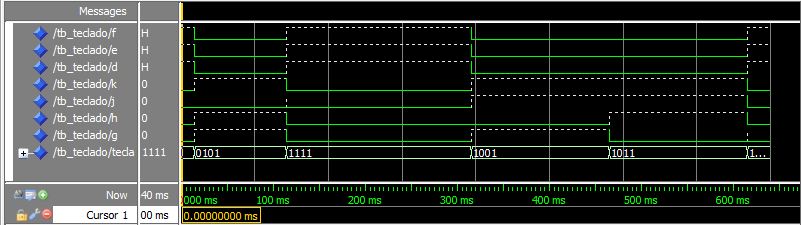

O resultado da simulação no Modelsim-Altera é o apresentado na figura a seguir:

Figura 4: Resultado da simulação no Modelsim-Altera.

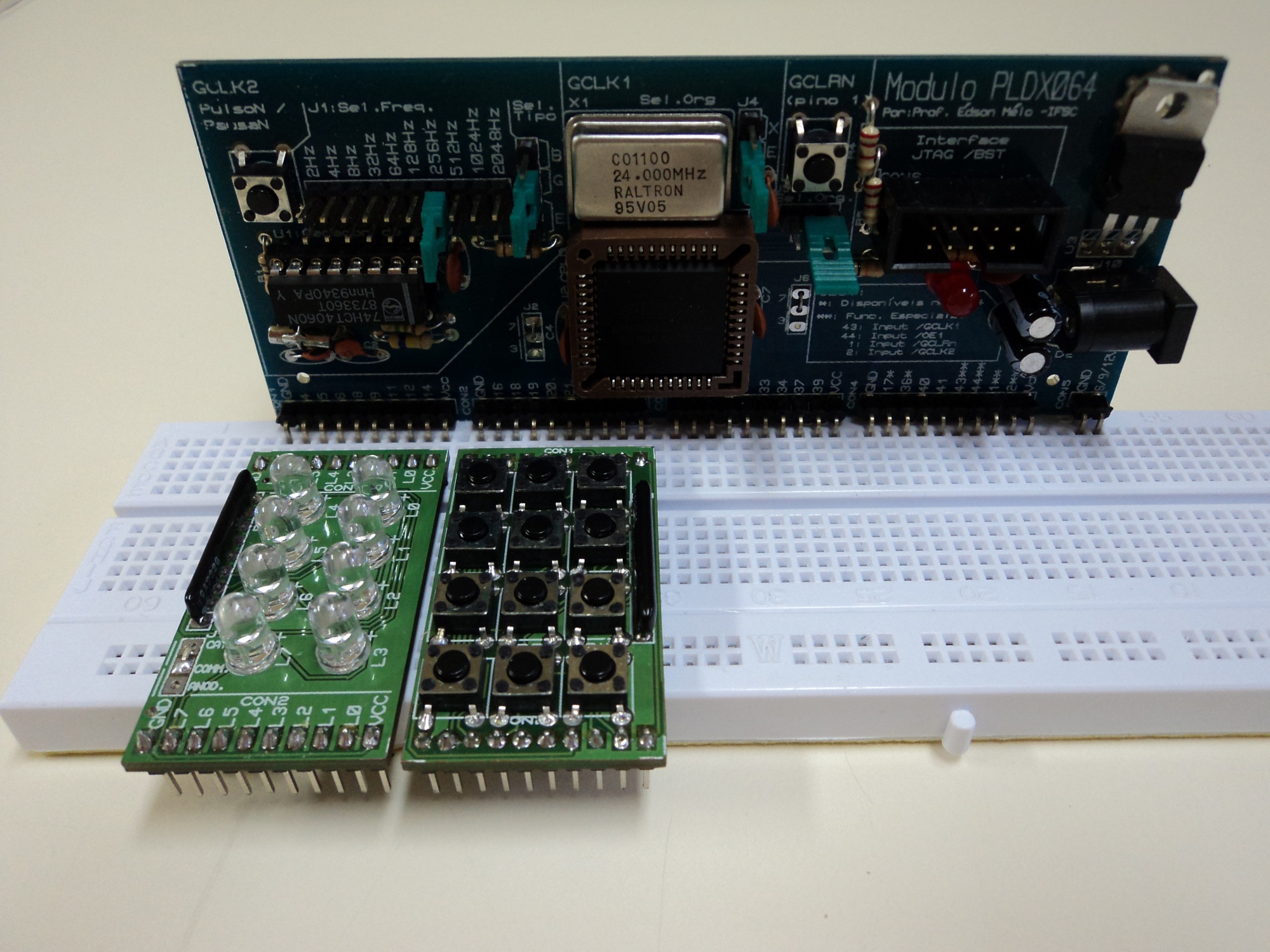

Estrutura Física

O projeto é composto pelo módulo do teclado, que será conectado no conector CON2 do Módulo CPLD_7064, e a placa LEDs, que será conectada no CON1, como mostrado na figura 5. Lembrando que o CPLD utilizado é o EPM7064, da família MAX7000S.

Figura 5: Montagem do projeto.

Montagem e Roteamento

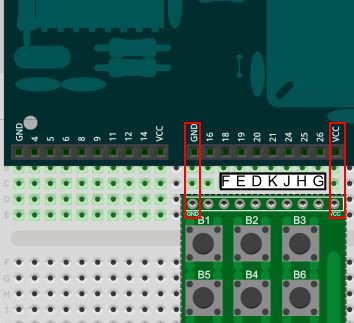

Como vimos acima, o teclado será colocado no conector CON2. Com base nisso e sabendo a pinagem do teclado pode-se rotear os pinos para a gravação do programa. As linhas K, J, H, G correspondem, respectivamente, aos pinos 21, 24, 25 e 26 e as colunas a F, E, D aos pinos 18, 19, 20.

Figura 6: Conexão entre teclado e o módulo CPLD

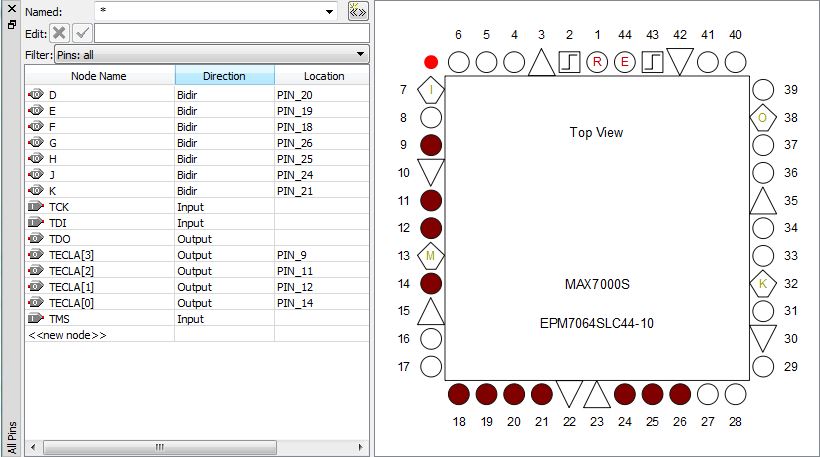

A placa de LEDs mostrará o valor do teclado lido pelo CPLD (sinal de saída TECLA). Sabendo da pinagem da placa de LEDs e que será colocada no conector CON1, como mostra a figura 5 (não se esqueça de conferir que o Vcc da placa se conecta ao Vcc do CPLD e da mesma forma o GND), podemos atribuir, de L3 a L0, respectivamente os pinos 9, 11, 12 e 14. A figura 8 mostra a lista com a atribuição de pinos (pin planer).

Figura 7: Conexão da placa de LEDs no módulo CPLD.

Figura 8: Atribuição dos pinos do projeto.

Gravação e Teste

Para gravar basta seguir o processo de gravação explicado no tutorial sobre o Quartus II© . Após gravar o código, basta montar o circuito como na figura 5, pressionar os botões e verificar se os LEDs acendem segundo o número binário correspondentes, como mostra o video no inicio da página.