Decodificador de Senha

- Detalhes

- Categoria: Exemplos com CPLD

- Publicado em Sexta, 09 Março 2012 09:23

- Escrito por João Marcos de Aguiar

- Acessos: 3648

Decodificador de Senha

O projeto apresentado nesse artigo tem como objetivo implementar sistema que lerá um teclado e, quando a sequência correta de digitos for digitada, acenderá um LED durante 15s.

O projeto foi desenvolvido em VHDL e testado via testbench no modelsim-Altera. Esse projeto é um exemplo de logica sequencial.

O equipamento utilizado foi:

- 1x Kit CPLD_7064;

- 1x placa teclado matricial;

- 1x placa de LEDs;

Descrição de Funcionamento

O decodificador de senha é baseado na leitura de teclado e, caso seja inserido a sequencia correta, sinaliza através de um LED, que ficará aceso por 15 segundos e depois desligará. A leitura de teclado é baseada na varredura de teclado matricial, a qual será utilizada como componente (caso não saiba como criar um componente em VHDL, siga as instruções dessa animação ).

Descrição em VHDL

Serão utilizadas apenas 10 portas, 7 para as linhas e colunas do teclado, 1 para o clock, 1 para reset e uma para a saida. Abaixo segue a declaração da entity:

Dentro da arquitetura teremos que declarar o componente da leitura do teclado e o sinal auxiliar TECLA para o registro da tecla pressionada.

Depois de declarar o componente, é feita a sua instanciação. Lembrando que é necessario que os signals/valores atribuidos sejam do mesmo tipo e do mesmo tamanho.

O process principal será sensível a variação do clock e do reset. Dentro do process são declaradas as variaveis que auxiliaram no controle do programa.

A primeira condição testada dentro do process é se o botão de reset está pressionado, caso esteja, os signals e variables do programa voltam aos valores iniciais.

Em seguida, é declarada a parte principal do programa, chamada a cada pulso de clock. A primeiramente verifica-se se a saída está ativa. Quando ela está ativa, incrementa-se a variable CONTA, responsável por limitar o tempo em que a saída ficará ativa, nesse caso 15 segundos, com um clock de 64Hz, o que da 960 contagens.

A variable CONT é responsável pela proteção contra o ruído de trepidação. A FLAG é indica se o botão anteriormente pressionado foi solto, para evitar que seja registrado mais de uma vez. Juntando essas duas variable mais o signal TECLA, que indica qual a tecla pressionada, constroi-se a condição necessária para a que seja registrado um valor na variable SENHA. O valor da senha pode ser modificado alterando o valor presente no if, neste caso a senha é colocada como x"0123".

A variable digito tem o objetivo de contar quantas teclas ja foram pressionadas e quando ja tiverem sido inseridas 4 teclas faz-se a verificação da senha, caso esteja correta a saida é habilitada. Depois disso, as variáveis são resetadas.

Fora do controle das teclas pressionadas, ocorre o incremento de CONT a cada pulso de clock.

Por ultimo, o programa verifica se as teclas do teclado estão soltas para fazer o controle da variable FLAG e atribui VALOR_SAIDA à SAIDA.

Simulação

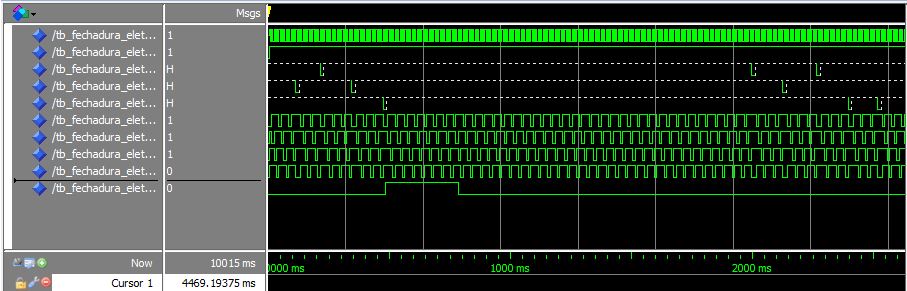

A simulação é feita através de um testbench que emula o pressionamento de uma sequência de teclas para averiguar o funcionamento do decodificador. Para que a simulação seja mais suscinta, diminui-se os limites de CONT e CONTA. Para este teste, modificou-se o limite de CONT para 1 e o de CONTA para 30.

As instruções do testbench iniciam com a geração do clock:

No outro processo são emulados o pressionamento dos botões. Abaixo segue a declaração para o pressionamento das primeiras teclas:

As formas de onda encontradas na simulação mostram o funcionamento correto do programa.

Figura 1: Resultados da Simulação.

Estrutura Física

O projeto é composto do kit CPLD_7064, um teclado matricial e uma placa de LEDs. O teclado funcionará como entrada de dados para a verificação da senha e a placa de LEDs, que apresentará a saída. O componente utilizado foi o EPM7064, da família MAX7000S.

Montagem e Roteamento

A placa de LEDs será conectada a CON1 e o LED escolhido para será o L0, portanto o pino correspondente no CPLD é o 14. O teclado será conectado a CON2 e tem a ordem de conexão segundo a imagem abaixo. Vale lembrar que o seletor de clock de baixa frequência deve estar na posição 64Hz.

Figura 3: Ilustração da conexão entre o teclado e o kit CPLD feita no Fritzing.

Figura 4 : Ilustração das conexões das placas periféricas com o kit CPLD feita no Fritzing.

Figura 5: Pin Planner com os pinos atribuidos.

Gravação e Teste

A gravação ocorre seguinto o tutorial do Quartus II. Para testar, pressiona-se as teclas e, caso a sequencia seja a correspondente a senha, o LED da saída acende. Esse mesmo algoritimo poderia ser usado para outras finalidades, como, por exemplo, uma fechadura acionada por senha, porém seria necessário implementar a comunicação entre o CPLD e a fechadura.