Memoria Ram em FPGA - Placa DE0

- Detalhes

- Categoria: Exemplos com FPGA

- Publicado em Quarta, 28 Setembro 2011 17:41

- Escrito por João Marcos de Aguiar

- Acessos: 4234

Memoria RAM em FPGA

Nesse artigo será apresentado um programa em VHDL utilizado para a escrita e leitura de uma memória RAM implementada dentro de um FPGA (CICLONE III), presente na placa de desenvolvimento DE0 . Para a implementação da memória utilizou-se a ferramenta de megafunções do QUARTUS© II. Devido a limitação da quantidade de pinos disponíveis, optou-se por não disponibilizar a entrada de endereços, somente a entrada de dados. Os endereços de escrita e leitura serão independentes e serão incrementados a cada escrita e leitura, respectivamente. Este exercício tem como objetivo a familiarização com as lógicas de escrita e leitura utilizadas por uma memória RAM. Este programa será simulado utilizando o Modelsim-Altera, por meio de um testbench.

Nesse projeto será utilizado apenas a Placa DE0®.

Descrição do Funcionamento

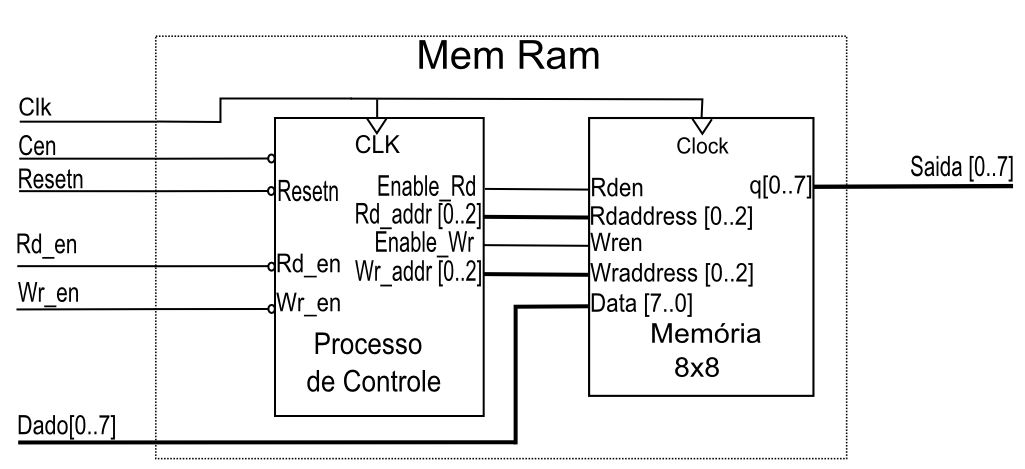

A memória criada com a ferramenta de Mega-Wizard Plug-in Manager do QUARTUS® II (Para aprender como criar megafunções clique aqui) possui 2 portas de endereços, uma para leitura e outra para escrita, uma porta para clock, 8 portas de entrada de dados, 8 portas de saída de dados, uma porta de habilitação de leitura e uma porta de habilitação de escrita. O programa de controle de leitura e escrita vai identificar se alguma das ações está habilitada, quando a escrita está habilitada, atribui-se o valor do dado de entrada do projeto a posição correspondente ao endereço de escrita. De forma similar, quando a leitura está habilitada, é atribuido à saida o valor correspondente a posição do endereço de leitura. O diagrama de blocos abaixo ilustra o funcionamento do projeto:

Figura 2: Diagra de blocos do projeto implementado.

Descrição em VHDL

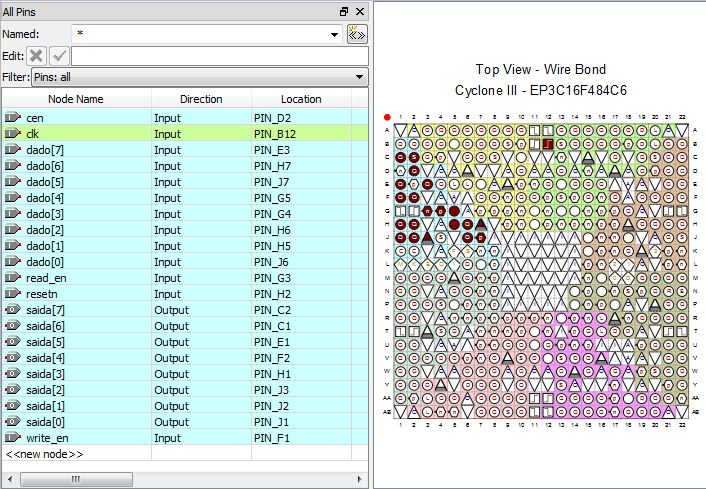

O projeto utiliza a placa DE0, utilizando 21 portas do FPGA, sendo uma para clock, uma para reset, uma para habilitação de leitura, uma para habilitação de escrita, uma para habilitação do chip, 8 para as entradas de dados e 8 para as saídas de dados. Abaixo está a declaração da entidade:

No inicio da arquitetura é declarado o componente criado por megafunção:

O sinais usados neste projeto servem para determinar qual o endereço que será lido/escrito pela/na memória. Os sinais de enable são usados para a habilitação da memoria.

O process principal pode ser dividido em 4 partes, reset, proteção contra ruído, escrita e leitura. Sendo que a leitura e a escrita podem ocorrer concorrentemente.

Na rotina de resete, atribui-se os valores iniciais para as variáveis e sinais.

A proteção contra ruído serve para rejeitar o ruído de trepidação decorrente dos push bottons presentes na placa e utilizados como sinais de enable.

A parte de escrita apresenta três variáveis de controle: habilitação de escrita, flag de escrita e a variavel de proteção contra ruído. A habilitação de escrita verififica a requisição de uma escrita. A flag evita que sejam escritos em mais de um endereço por requisição de escrita. Por ultimo, como ja foi explicado, a variável de proteção contra ruído para eliminar os efeitos do ruído de trepidação.

A rotina de leitura funciona de forma analoga a rotina de escrita.

No final de processo há a passagem dos valores das variáveis para os sinais.

Por ultimo, faz-se a instanciação da memória, atribuindo os sinais da seguinte forma:

Simulação

Para a simulação do projeto, emulou-se a gravação de todos os 8 endereços de memória, atribuindo valores de 1 a 8. Em seguida, fez-se as leituras dos endereços para averiguar o funcionamento da memória. Como a leitura e escrita são síncronas, também emulou-se o clock. O código abaixo apresenta as primeiras linhas do testbench:

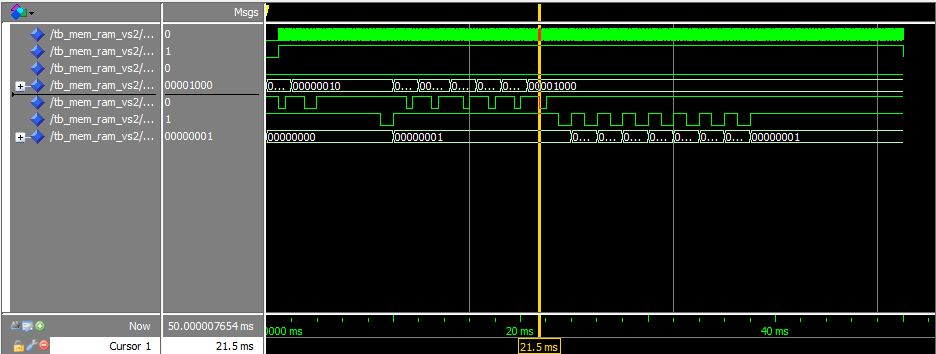

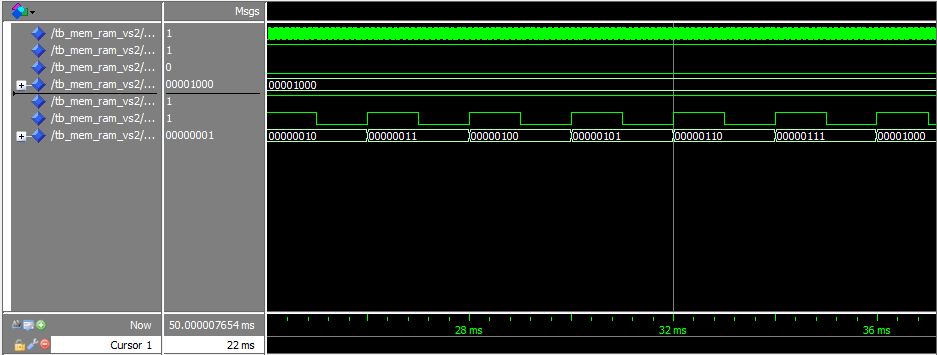

As formas de ondas encontradas na simulação com o Modelsim®-Altera estão apresentadas abaixo:

Figura 3: Formas de ondas da simulação.

Figura 4: Detalhe dos dados lidos

Estrutura Física

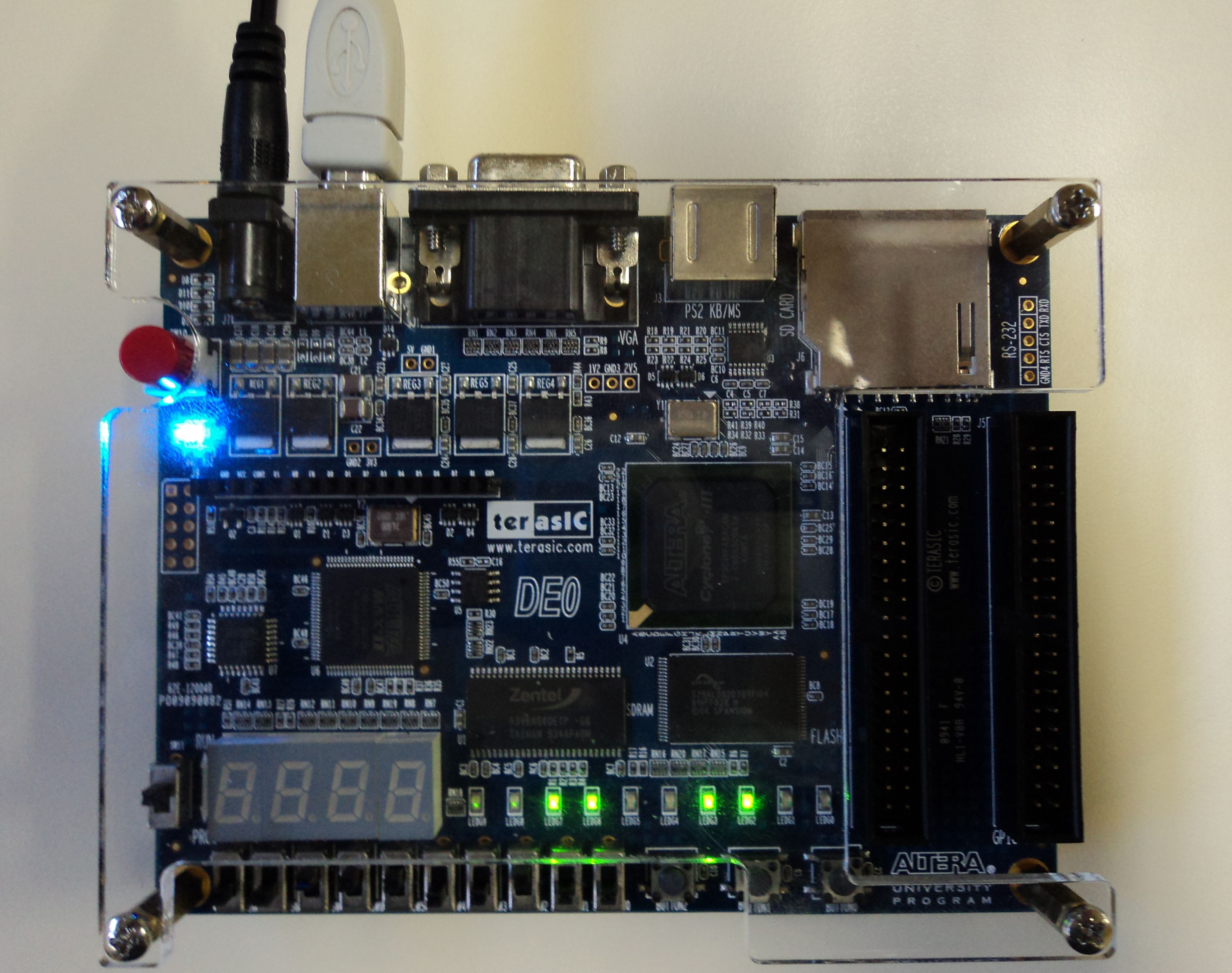

Figura 5: Projeto implementado na placa DE0®.

O projeto é composto apenas pela placa DE0, em usa os 8 LEDs como sendo a saída da memória, 9 switches, 8 como entrada de dados e 1 como pino de chip enable, e 3 push bottoms, 1 como resete, 1 como habilitação de escrita e 1 como habilitação de leitura. A pinagem utilizada está apresentada abaixo, utilizando como base o manual do usuário da placa DE0.

Figura 6: Atribuição de pinos do projeto.

Gravação e Teste

Para fazer o teste basta gravar o programa seguindo as intruções encontradas no tutorial ou no próprio manual da placa DE0. Em seguida basta dar os comandos de gravação e leitura e observar o resultado. O teste pode ser observado no video no início da página.

Arquivos de Projeto

Links

- Site oficial DE0 (Inglês).